- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

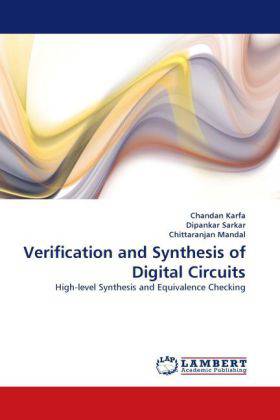

Verification and Synthesis of Digital Circuits

High-level Synthesis and Equivalence Checking

Chandan Karfa, Dipankar Sarkar, Chittaranjan Mandal

Paperback | Engels

€ 99,45

+ 198 punten

Omschrijving

Advances in VLSI technology have enabled its deployment into complex circuits. Synthesis flow of such circuits comprises various phases where each phase performs the task algorithmically providing for ingenious interventions of experts. The gap between the original behaviour and the finally synthesized circuit is too wide to be analyzed by any reasoning mechanism. The validation tasks, therefore, must be planned to go hand-in-hand with each phase of synthesis with scope to handle the special characteristics of each synthesis sub-task separately. This book is concerned with hand-in-hand verification and (high-level) synthesis of digital circuits. The verification problem is formulated as equivalence checking between two finite state machines with data-paths (FSMD). The difficulties of each phase are identified and the verification methods based on equivalence of two FSMDs have been formulated accordingly. A high-level synthesis tool, called structured architecture synthesis tool (SAST), has been developed which support hand-in-hand synthesis and verification.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 204

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783838398136

- Verschijningsdatum:

- 30/08/2010

- Uitvoering:

- Paperback

- Afmetingen:

- 152 mm x 229 mm

- Gewicht:

- 304 g

Alleen bij Standaard Boekhandel

+ 198 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.