- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

€ 111,95

+ 223 punten

Omschrijving

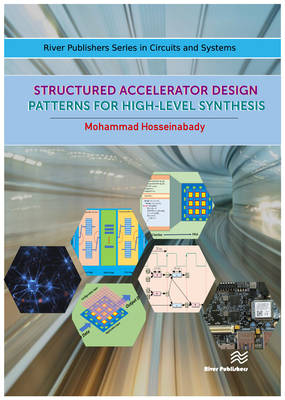

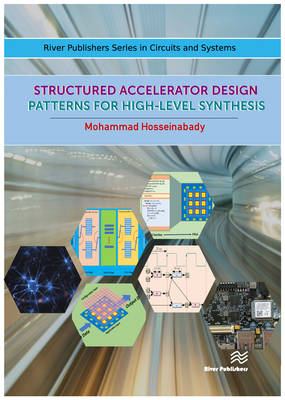

Accelerators now play a crucial role in computing systems. With the emergence of a new wave of academic and industrial high-level synthesis (HLS) tools, FPGA-based accelerators now are more accessible to software programmers. However, there are several burdens placed upon the programmers to design a high-performance accelerator when using FPGA, such as different memory and parallel programming models. Therefore, a high-level structured design approach targeting accelerator is essential. This approach advances software programming techniques to utilise FPGAs efficiently. This book explains the concept of accelerator design using current high-level synthesis tools and techniques. It describes different types of regular and irregular accelerator patterns as a structured building block for FPGA implementation. The cutting-edge programming models based on C/C++ and OpenCL are used to explain standard computation and memory patterns through many examples and case studies. In short, this book - offers theory and practice of HLS parallel programming techniques for FPGA - describes parallel patterns for regular and irregular algorithms - contains detailed examples in C/C++ and OpenCL for HLS - represents the efficiency of FPGA accelerators through several case studies in scientific computation and machine learning areas

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 300

- Taal:

- Engels

- Reeks:

Eigenschappen

- Productcode (EAN):

- 9788770223959

- Verschijningsdatum:

- 30/09/2022

- Uitvoering:

- Hardcover

- Formaat:

- Genaaid

- Afmetingen:

- 152 mm x 229 mm

Alleen bij Standaard Boekhandel

+ 223 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.