- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

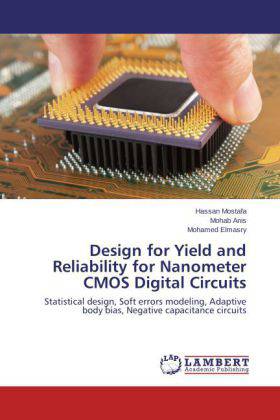

Design for Yield and Reliability for Nanometer CMOS Digital Circuits

Statistical design, Soft errors modeling, Adaptive body bias, Negative capacitance circuits

Hassan Mostafa, Mohab Anis, Mohamed Elmasry

Paperback | Engels

€ 59,45

+ 118 punten

Omschrijving

The nano-age has already begun, where typical feature dimensions are smaller than 100nm. The operating frequency is expected to increase up to 12 GHz, and a single chip will contain over 40 billion transistors in 2020, as given by the International Technology Roadmap for Semiconductors (ITRS) initiative. ITRS also predicts that the scaling of CMOS devices and process technology, as it is known today, will become much more difficult as the industry advances towards the 16nm technology node and further. This aggressive scaling of CMOS technology has pushed the devices to their physical limits. Design goals are governed by several factors other than power, performance and area such as process variations, radiation induced soft errors, and aging degradation mechanisms. These new design challenges have a strong impact on the parametric yield and reliability of nanometer digital circuits and also result in functional yield losses in variation-sensitive digital circuits such as Static Random Access Memory (SRAM) and flip-flops.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 296

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783659513619

- Verschijningsdatum:

- 26/01/2014

- Uitvoering:

- Paperback

- Afmetingen:

- 150 mm x 220 mm

- Gewicht:

- 435 g

Alleen bij Standaard Boekhandel

+ 118 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.