- Afhalen na 1 uur in een winkel met voorraad

- In januari gratis thuislevering in België

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- In januari gratis thuislevering in België

- Ruim aanbod met 7 miljoen producten

Zoeken

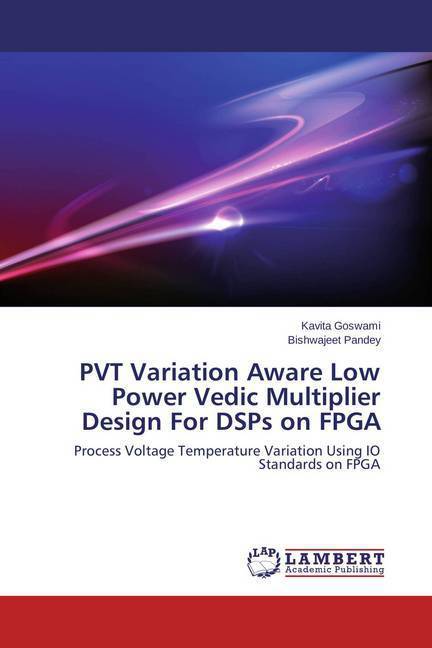

PVT Variation Aware Low Power Vedic Multiplier Design For DSPs on FPGA

Process Voltage Temperature Variation Using IO Standards on FPGA

Kavita Goswami, Bishwajeet Pandey

Paperback | Engels

€ 61,95

+ 123 punten

Omschrijving

As the communication and signal processing industries are proliferating the demand for the multipliers is continuously increasing at a rapid rate. For researchers, to develop high speed and power efficient multiplier has been a grave matter of concern. Reduction in the power consumption and delay of a multiplier circuitry is expected to cause a revolution in the field of electronics and communication.The performance of system is generally determined by the performance of the multiplier because the multiplier is generally the slowest element in the system. Hence, optimizing the speed and power consumption of the multiplier is a major design issue. There is need of development of high speed and low power multiplier for digital signal processing algorithms. From the previous research, it has been concluded that Vedic multiplier are more efficient than conventional multiplier. In this work, low power Vedic multiplier has been proposed.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 104

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783659629358

- Verschijningsdatum:

- 3/11/2014

- Uitvoering:

- Paperback

- Afmetingen:

- 150 mm x 220 mm

- Gewicht:

- 163 g

Alleen bij Standaard Boekhandel

+ 123 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.