Je cadeautjes zeker op tijd in huis hebben voor de feestdagen? Kom langs in onze winkels en vind het perfecte geschenk!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Je cadeautjes zeker op tijd in huis hebben voor de feestdagen? Kom langs in onze winkels en vind het perfecte geschenk!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

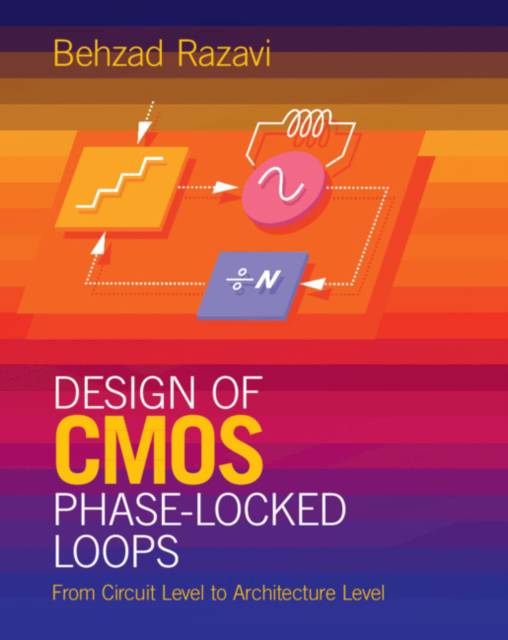

Design of CMOS Phase-Locked Loops

From Circuit Level to Architecture Level

Behzad Razavi

Hardcover | Engels

€ 169,45

+ 338 punten

Omschrijving

Using a modern, pedagogical approach, this textbook gives students and engineers a comprehensive and rigorous knowledge of CMOS phase-locked loop (PLL) design for a wide range of applications. It features intuitive presentation of theoretical concepts, built up gradually from their simplest form to more practical systems; broad coverage of key topics, including oscillators, phase noise, analog PLLs, digital PLLs, RF synthesizers, delay-locked loops, clock and data recovery circuits, and frequency dividers; tutorial chapters on high-performance oscillator design, covering fundamentals to advanced topologies; and extensive use of circuit simulations to teach design mentality, highlight design flaws, and connect theory with practice. Including over 200 thought-provoking examples highlighting best practices and common pitfalls, 250 end-of-chapter homework problems to test and enhance the readers' understanding, and solutions and lecture slides for instructors, this is the perfect text for senior undergraduate and graduate-level students and professional engineers who want an in-depth understanding of PLL design.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 506

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9781108494540

- Verschijningsdatum:

- 30/01/2020

- Uitvoering:

- Hardcover

- Formaat:

- Genaaid

- Afmetingen:

- 208 mm x 254 mm

- Gewicht:

- 1360 g

Alleen bij Standaard Boekhandel

+ 338 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.